集成电路版图设计就是指将电路设计电路图或电路描述语言映射到物理描述层面,从而可以将设计好的电路映射到晶圆上生产。版图是包含集成电路的器件类型,器件尺寸,器件之间的相对位置以及各个器件之间的连接关系等相关物理信息的图形,这些图形由位于不同绘图层上的图形构成。集成电路设计方法涉及面广,内容复杂,其中版图设计是集成电路物理实现的基础技术。

根据使用的温度范围(军用-55~125℃,民用-25~85℃)及其他可靠性要求,版图设计需要考虑电性能和热性能。由电参数要求及工艺水平来确定元件的结构、尺寸,再考虑寄生效应、散热等问题,从而最后确定整个电路的布局和布线。下面提高集成电路版图设计中的可靠性一般采取的措施。

_20210723170820_801.jpg)

1、关于金属化层布线

大量的失效分析表明,因金属化层(目前一般是Al层)通过针孔和衬底短路,且Al膜布线开路造成的失效不可忽视,所以必须在设计布线时采取预防措施。例如尽量减少Al条覆盖面积,采用最短Al条,并尽量将Al条布在厚氧化层(厚氧化层寄生电容也小)上以减少针孔短路的可能。

防止Al条开路的主要方法是尽量少的通过氧化层台阶。如果必须跨过台阶,则采取减少台阶高度和坡度的办法。

为防止Al条电流密度过大造成的电迁移失效,要求设计时通过Al条的电流密度J<2×10^5A/cm2,Al条要有一定的宽度和厚度。

对于多层金属布线,版图设计中布线层数及层与层之间通道应尽可能少。

2、版图设计中的热分布问题

据推测,芯片温度每提高25℃失效率约增加一倍,所以要尽量降低芯片温度以降低失效率。为防止结温过高,功率较大的管子面积要设计得足够大,而发射区有效边长仍由最大电流确定。在整个芯片上发热元件的布局分布要均匀,不使热量过分集中在一角。在元件的布局上,还应将容易受温度影响的元件远离发热元件布置。在必须匹配的电路中,可把对应的元件并排配置或轴对称配置,以避免光刻错位和扩散不匀。要注意电源线和地线的位置,这些布线不能太长。

3、其他措施

(1)元件尺寸的选择要适当。应考虑功率密度、寄生效应、制版光刻误差、横向扩散及扩散容差等因素,Al条应覆盖欧姆接触孔并留一定余量。

(2)保证电路参数的要求:多发射极晶体管的长脖子区不宜太长,因为太长会导致fT下降;避免在输出线上做扩散“地”道;外延层电阻岛上接电源的欧姆接触孔要扩n+。

此外,对于CMOS集成电路,为提高其抗闩锁能力可在版图设计上采取以下措施:①合理布置电源接触孔,减小横向电流密度和横向电阻;②采用接衬底的环形VDD电源线(p阱),并尽可能将衬底背面接VDD;③增加电源VDD和VSS(GND)接触孔,并加大接触面积;④对每一个接VDD的孔都要在相邻的阱中配以对应的VSS(GND)接触孔,以便增加并行的电流通路;⑤尽量使VDD和VSS的接触孔的长边相互平行;⑥接VDD的孔尽可能安排得离阱远一些;⑦接VSS的孔要尽可能安排在p阱的所有边上。

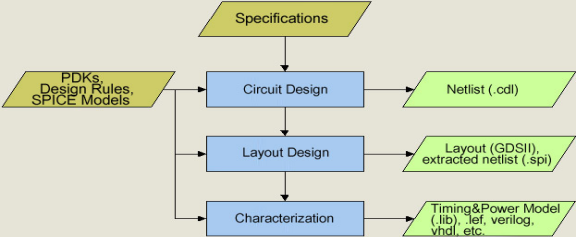

集成电路版图设计规则的作用是保证电路性能,易于在工艺中实现,并能取得较高的成品率。版图设计的质量好坏直接会影响到集成电路的功耗、性能和面积。在系统芯片(system-on-chip, SoC)设计中,集成了接口单元(input/output,I/O),标准逻辑单元(standard cell),模拟与混合信号(analog mixed-signal, AMS)模块,存储器(memory,例如ROM,RAM)和多种IP模块。所有这些模块的物理实现,全都离不开基本的版图设计。工程实践中,从定义系统芯片参数(specifications)完成后,人们常常将最常见的数字集成电路中标准逻辑单元的版图设计过程简化为电路设计(circuit design)、版图设计(layout design)和特征化(characterization)等三个步骤,见图1简化的版图设计流程图。在实践中,版图设计类型又分为: 1)标准版图设计,2)半定制版图设计,和3)全定制版图设计。

总结:无论是标准单元版图设计,半定制版图设计和全定制版图设计,基本的设计方法得到发扬传承,高性能、低功耗、低成本的要求提得更高,对未来高质量高可靠性版图设计设立了新的规范和起点。